Verilog has system tasks and functions that can open files, output values into files, read values from files and load into other variables and close files.

Opening and closing files

module tb;

// Declare a variable to store the file handler

integer fd;

initial begin

// Open a new file by the name "my_file.txt"

// with "write" permissions, and store the file

// handler pointer in variable "fd"

fd = $fopen("my_file.txt", "w");

// Close the file handle pointed to by "fd"

$fclose(fd);

end

endmodule

Most programming languages have a characteristic feature called scope which defines the visibility of certain sections of code to variables and methods. The scope defines a namespace to avoid collision between different object names within the same namespace.

Verilog defines a new scope for modules, functions, tasks, named blocks and generate blocks.

module tb;

reg signal;

// Another variable cannot be declared with

// an already existing name in the same scope

reg signal;

// However, the name 'signal' can be reused inside

// a task because it belongs to a different scope.

task display();

reg signal = 1;

$display("signal = %0b", signal);

endtask

endmodule

An identifier, like a signal name, can be used to declare only one type of item in a given scope. This means that two variables of different or same data types cannot have the same name, or a task and a variable of the same name, or even a net and gate instance with the same name in the same scope.

Verilog math functions can be used in place of constant expressions and supports both integer and real maths.

Integer Math Functions

The function $clog2 returns the ceiling of log2 of the given argument. This is typically used to calculate the minimum width required to address a memory of given size.

For example, if the design has 7 parallel adders, then the minimum number of bits required to represent all 7 adders is $clog2 of 7 that yields 3.

module des

#(parameter NUM_UNITS = 7)

// Use of this system function helps to reduce the

// number of input wires to this module

(input [$clog2(NUM_UNITS)-1:0] active_unit);

initial

$monitor("active_unit = %d", active_unit);

endmodule

`define NUM_UNITS 5

module tb;

integer i;

reg [`NUM_UNITS-1:0] active_unit;

des #(.NUM_UNITS(`NUM_UNITS)) u0(active_unit);

initial begin

active_unit = 1;

#10 active_unit = 7;

#10 active_unit = 8;

end

endmodule

Note that the signal active_unit has 3-bits to store total 5 units.

Clocks are fundamental to building digital circuits as it allows different blocks to be in sync with each other.

Properties of a clock

The key properties of a digital clock are its frequency which determines the clock period, its duty cycle and the clock phase in relation to other clocks.

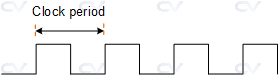

Clock Period

The frequency indicates how many cycles can be found in a certain period of time. And hence the clock period is the time taken to complete 1 cycle.

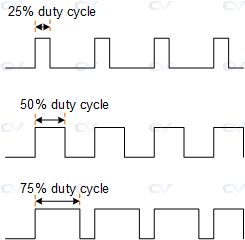

Clock Duty Cycle

The amount of time the clock is high compared to its time period defines the duty cycle.

Multi-bit Verilog wires and variables can be clubbed together to form a bigger multi-net wire or variable using concatenation operators { and } separated by commas. Concatenation is also allowed to have expressions and sized constants as operands in addition to wires and variables.

Size of each operand must be known in order to calculate the complete size of concatenation.

Verilog Concatenation Example

wire a, b; // 1-bit wire

wire [1:0] res; // 2-bit wire to store a and b

// res[1] follows a, and res[0] follows b

assign res = {a, b};

wire [2:0] c;

wire [7:0] res1;

// res[0] follows c[2]

// res[2:1] is always 0

// res[4:3] follows c[1:0]

// res[5] follows a

// res[6] follows b

assign res1 = {b, a, c[1:0], 2'b00, c[2]};