What are SystemVerilog threads or processes ?

A thread or process is any piece of code that gets executed as a separate entity. In verilog, each of the initial and always blocks are spawned off as separate threads that start to run in parallel from zero time. A fork join block also creates different threads that run in parallel.

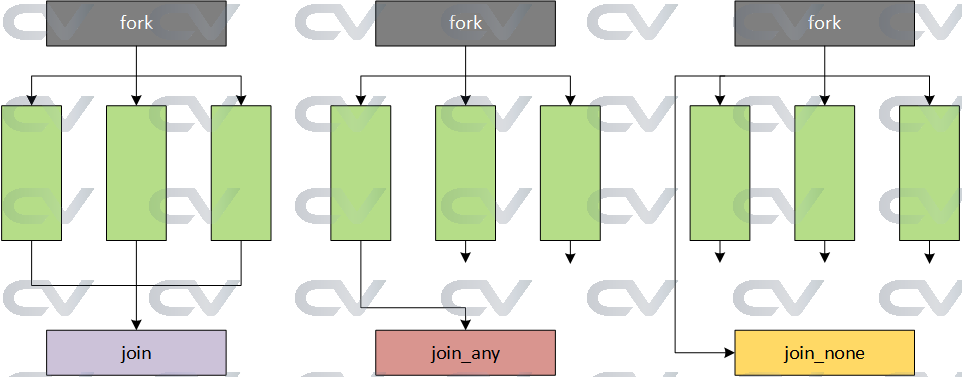

What are different fork - join styles ?

We have three different styles of fork join in SystemVerilog.

Why do we need randomness in the environment ?

Directed tests take a long time to develop because you have to think about all possible scenarios to verify different features. There is a high possibility that you would miss some kind of corner cases. So we want to be able to generate random values that fall within a valid range and apply these random values to the signals we are interested in.

What are classes ?

class is a user-defined datatype, an OOP construct, that can be used to encapsulate data (property) and tasks/functions (methods) which operate on the data. Here's an example:

class myPacket;

bit [2:0] header;

bit encode;

bit [2:0] mode;

bit [7:0] data;

bit stop;

function new (bit [2:0] header = 3'h1, bit [2:0] mode = 5);

this.header = header;

this.encode = 0;

this.mode = mode;

this.stop = 1;

endfunction

function display ();

$display ("Header = 0x%0h, Encode = %0b, Mode = 0x%0h, Stop = %0b",

this.header, this.encode, this.mode, this.stop);

endfunction

endclass

What is an Interface ?

An Interface is a way to encapsulate signals into a block. All related signals are grouped together to form an interface block so that the same interface can be re-used for other projects. Also it becomes easier to connect with the DUT and other verification components.

Example

APB bus protocol signals are put together in the given interface. Note that signals are declared within interface and endinterface.

interface apb_if (input pclk);

logic [31:0] paddr;

logic [31:0] pwdata;

logic [31:0] prdata;

logic penable;

logic pwrite;

logic psel;

endinterface

Why are signals declared logic ?

logic is a new data type that lets you drive signals of this type via assign statements and in a procedural block. Remember that in verilog, you could drive a reg only in procedural block and a wire only in assign statement. But this is only one reason.

Signals connected to the DUT should support 4-states so that X/Z values can be caught. If these signals were bit then the X/Z would have shown up as 0, and you would have missed that DUT had a X/Z value.

break

module tb;

initial begin

// This for loop increments i from 0 to 9 and exit

for (int i = 0 ; i < 10; i++) begin

$display ("Iteration [%0d]", i);

// Let's create a condition such that the

// for loop exits when i becomes 7

if (i == 7)

break;

end

end

endmodule

ncsim> run Iteration [0] Iteration [1] Iteration [2] Iteration [3] Iteration [4] Iteration [5] Iteration [6] Iteration [7] ncsim: *W,RNQUIE: Simulation is complete.

continue

module tb;

initial begin

// This for loop increments i from 0 to 9 and exit

for (int i = 0 ; i < 10; i++) begin

// Let's create a condition such that the

// for loop

if (i == 7)

continue;

$display ("Iteration [%0d]", i);

end

end

endmodule

ncsim> run Iteration [0] Iteration [1] Iteration [2] Iteration [3] Iteration [4] Iteration [5] Iteration [6] Iteration [8] Iteration [9] ncsim: *W,RNQUIE: Simulation is complete.